Логические вентили — это базовые строительные блоки цифровых схем, выполняющие простейшие логические операции над входными сигналами. Наиболее распространённые типы вентилей — И (AND), ИЛИ (OR) и НЕ (NOT). Каждый из них реализует базовую логическую функцию: вентиль И выдаёт единицу, только если на всех входах единица; вентиль ИЛИ — если хотя бы один вход равен единице; вентиль НЕ инвертирует входной сигнал. Эти три элемента считаются функционально полными, поскольку из их комбинаций можно построить любую цифровую схему.

Помимо базовых вентилей, широко применяются составные элементы: И-НЕ (NAND), ИЛИ-НЕ (NOR), исключающее ИЛИ (XOR) и его инверсия (XNOR). Вентили NAND и NOR особенно важны в цифровом проектировании, так как каждая из этих операций также является функционально полной, а значит, может использоваться для создания любых логических функций без привлечения других типов вентилей. XOR применяется там, где требуется сравнение битов, сложение по модулю два и построение схем чётности.

Тип вентилей влияет не только на функциональность схемы, но и на её технические характеристики — скорость, энергопотребление и надёжность. Современные логические элементы выпускаются в виде интегральных микросхем с различными логическими семействами (TTL, CMOS и др.), каждая из которых имеет свои особенности. Выбор конкретного типа вентилей и технологии зависит от требований к устройству: частоты работы, числа входов, плотности интеграции и условий эксплуатации.

Построение комбинированных схем

Комбинированные схемы — это цифровые устройства, в которых выходные сигналы зависят только от текущих входных данных, без учёта предыдущего состояния. Они формируют логические функции, объединяя вентили в структуры, способные выполнять арифметические, логические или управляющие операции. Построение таких схем начинается с формального описания задачи, часто в виде таблицы истинности или логического выражения, на основе которых проектируется структура из логических вентилей.

На этапе синтеза схемы важно упростить логическое выражение, чтобы сократить количество элементов и улучшить надёжность и быстродействие. Для этого применяются методы булевой алгебры и графические способы минимизации, например, карты Карно. Упрощённая логическая функция реализуется с использованием базовых или составных вентилей, при этом проектировщик стремится минимизировать количество уровней логики — чем меньше каскадов, тем быстрее работает схема.

Примерами комбинированных схем являются сумматоры, дешифраторы, мультиплексоры, компараторы и арифметико-логические устройства (АЛУ). В каждой из них применяются различные принципы объединения вентилей, чтобы выполнять сложные операции. Например, четырёхбитный сумматор может быть построен путём последовательного соединения однобитных сумматоров, в которых активно используется логика XOR и AND для вычисления суммы и переноса.

При проектировании важно учитывать задержки распространения сигнала, влияние фан-аута (числа вентилей, которые может управлять выход одного элемента) и потребление энергии. Ошибки на этом этапе могут привести к логическим сбоям, особенно при работе на высоких частотах. Поэтому отладка схемы с помощью симуляторов и макетирования остаётся важным этапом даже в цифровом проектировании. Грамотное построение комбинированных схем позволяет создавать надёжные и предсказуемые устройства для множества применений — от простой логики до сложных процессорных ядер.

Триггеры и счетчики

Триггеры — это базовые элементы последовательной логики, способные хранить один бит информации. В отличие от комбинированных схем, выходное состояние триггера зависит не только от текущих входных сигналов, но и от предыдущего состояния, что делает их фундаментом для построения запоминающих устройств и автоматов управления. Существуют разные типы триггеров: RS, JK, D и T — каждый из которых применяется в зависимости от нужной логики переключения и синхронизации.

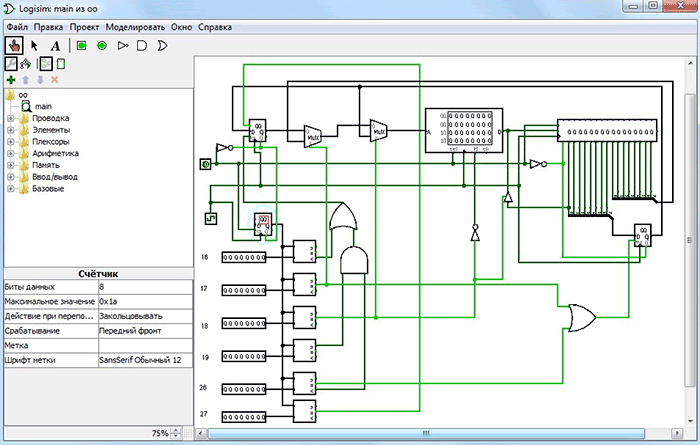

На основе триггеров строятся счётчики — устройства, предназначенные для подсчёта тактов, импульсов или событий. Они бывают синхронными, когда все триггеры переключаются одновременно, и асинхронными, где переключение происходит по цепочке. Счётчики широко применяются в таймерах, генераторах импульсов, делителях частоты и цифровых системах управления. Конструкция счётчиков может быть прямой, обратной или реверсивной, в зависимости от направления счёта.

Особое внимание при проектировании таких устройств уделяется синхронизации и подавлению дрожания сигналов. Поскольку счётчики работают на тактовых импульсах, важно обеспечить чистоту фронтов, чтобы избежать ложных срабатываний. Кроме того, схема должна обеспечивать надёжную установку начального состояния и иметь защиту от ошибок переполнения. Благодаря своей универсальности и простоте триггеры и счётчики остаются незаменимыми компонентами в цифровой электронике.

Тайминги и синхронизация

Тайминги и синхронизация — ключевые аспекты при проектировании цифровых схем, особенно последовательной логики. Тайминг определяет моменты изменения состояния элементов схемы относительно тактовых сигналов, а синхронизация обеспечивает согласованную работу всех частей устройства. Без правильного учета этих факторов цифровая схема может работать некорректно, допуская ошибки из-за несвоевременного переключения или конфликтов сигналов.

В основе синхронизации лежит тактовый генератор, который формирует регулярные импульсы для управления триггерами и другими запоминающими элементами. Важно, чтобы все элементы схемы имели одинаковую точку отсчёта времени, иначе данные могут «разъезжаться» по цепи и приводить к логическим ошибкам. Для этого используются методы распространения тактового сигнала по специальным линиям с минимальными задержками и искажениями.

Кроме того, при проектировании учитываются параметры задержек распространения сигналов внутри вентилей и триггеров, чтобы обеспечить корректный захват и передачу данных. Важной характеристикой является время установки (setup time) и время удержания (hold time), которые определяют минимальные интервалы, в течение которых входной сигнал должен оставаться стабильным перед и после фронта тактового сигнала. Нарушение этих условий приводит к метастабильности — состоянию неопределённости, которое снижает надёжность работы.

Для обеспечения надежной работы на высоких частотах применяются дополнительные методы — буферизация, использование фазовых автоподстройщиков частоты (PLL) и синхронизация асинхронных сигналов через специальные схемы. Правильное управление таймингами и синхронизацией позволяет создавать цифровые устройства с высокой скоростью, точностью и устойчивостью к внешним воздействиям, что особенно важно в процессорах, системах связи и автоматике.

Добавить комментарий